I2C 通信速度又两种:100kHZ\400KHZ\一般布超过1MHZ,如果时钟太快,低成本器件支撑不了这么快的速率。

Master 和slave 没有绝对关系。时钟输出的是Master。

UART则是双方对等的通信。

IIC 和SPI 都是不对等的,他们要分主从。

- I2C

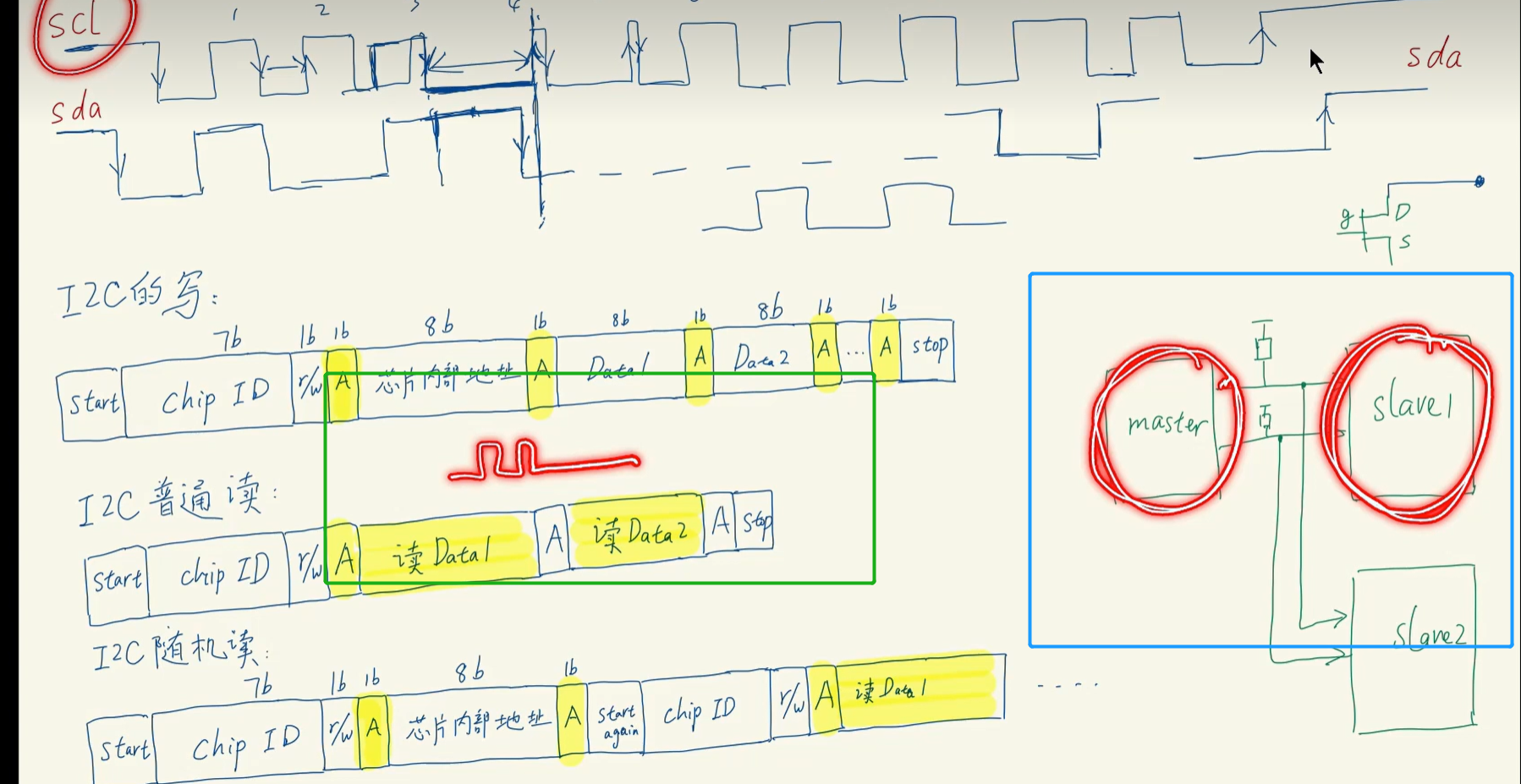

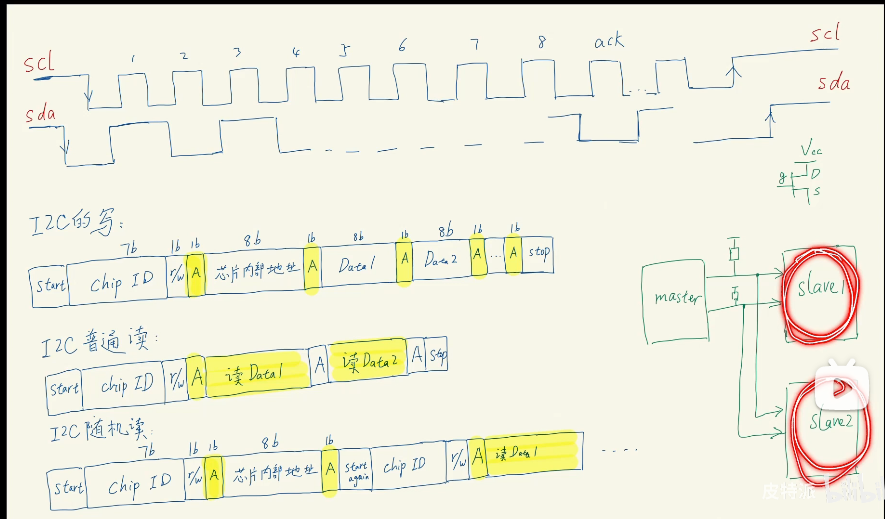

- 正常来讲I2C 的SCL时钟,高电平的时候 sda 不能做出交换。但是在开始和停止的时候,sda会在 scl 高电平时进行转换。

- start 信号发出之后,为了区分主从,会有7 bit 的chip ID 进行通信的确认,然后 会有一个 1 bit 的读写的电平(1为写,0 为读),交代好之后 会有一个 1bit的ack 确认位,之后会有一个8 bit芯片的内部地址,然后确认。之后ack , 然后进行数据交换。

TIP:chip ID确认和哪一个从芯片进行通信。别的slaver保持沉默。

- 在数据交换时候,它会根据初始地址进行 +1字节 的操作。每个数据为 8bit 。最后ACK之后才进行stop 操作。

ack 默认为1 高电平,当回复收到时会回复0.没收到就是默认1 高电平。

芯片可能有多个内部地址,当然需要用的时候 Data数据换成地址就行。

读的时候时chip ID后面一个电平为1.写则是为0

scl为1时,sda 出现上升沿就是stop。

scl为1时,sda 出现下降沿就是start。

写的话,slave要回复ack(0) ,然后再stop

读的话,master 要回复(也就是默认ACK 为1没收到。)nACK(1),然后再stop

- 普通读 根据写的最后一个地址,然后开始读。

随机读

需要读芯片的特定地址时,需要加入芯片内部地址,然后ACK ,之后!!!!start again 。如果太慢的话,可以stop 再start

在总线切换时,可能master slave都要争夺那两根总线。可能会发生红色的冲突。很正常。

I2C 深入了解

- 上图的 master 和 slave 为什么有2个上拉

- SCL 时钟能不能不是50% 占空比呢?什么占空比更好呢?

- slave 可以反作用于 master呢?因为master 控制着slave,slave可以声张它的权益吗?

- 如果设计芯片,设计slave I2C接口不想用 clock可以吗。

1.为什么要用上拉

芯片引脚也就pin 脚,使用的OD 开漏脚(open-drain) 脚,

MOS管是电压控制元件,三极管是电流控制元件。

三极管要注意直流放大系数。

PNP NPN级三极管,N级很多自由电子,P级很多空穴。

NPN 和PNP 区别:

为什么用上拉:因为 当 master 发送要获取 slave2 的数据是,如果slave1 回复nACK 那么SDA总线电压就会上拉,master就和slave1 建立通信了,所以设计的时候sda 总线使用开漏OD.(欲练此功,必先自宫,电压想上去还是得看master发话),slave弱上拉,

- mos图

slave 里面的 MOS 需要经过OD 开漏脚,导致slave 自身不能上拉电平。因为master 要接多个slave ,以免别的slave引起冲突。

2.时钟占空比一定百分之50?

不一定。

SCL 上升沿是抓取数据,下降沿是打印出数据。

器件如果特别好,延时比较低,可以SCL和SDA近乎同步。.

如果器件想要更高频率,那就把占空比降到最低!

如果元器件性能较差,延时较高,可以降低SCL 时钟的占空比,

3.slave 能否干预 master 的操作呢?(slave 伸张自己权益)

- 有一些器件允许反向操作master ,比如 master 的时钟管脚 既带输入又带输出功能,

- 具体操作方法: slave 造反,master 发送scl 时钟信号,slave 不回复,而且使用OD 将scl 时钟拉低到0 , 可以做到 slave 对master 的暂停。

slave 的数据没准备好,使用拉低 scl 时钟让master 停止请求,当准备好之后再恢复时钟 - 先决条件,master 和slave 的 SCL 都具备接收/发送的功能

不过master 有一个超时机制的操作,会认为 slave 会坏掉然后进行复位操作。

4.某系芯片能否不用scl 线?

可以不用,为了节约成本,但是。。。。。

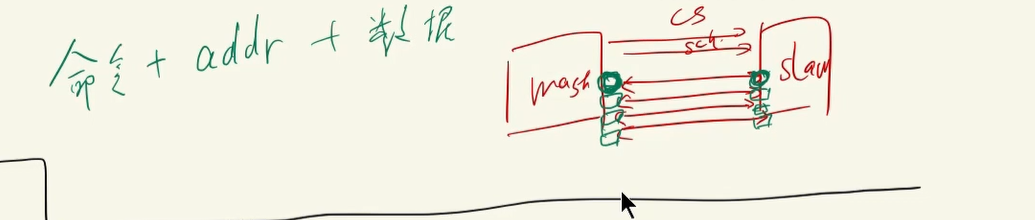

高速SPI接口 以及 flash 操作

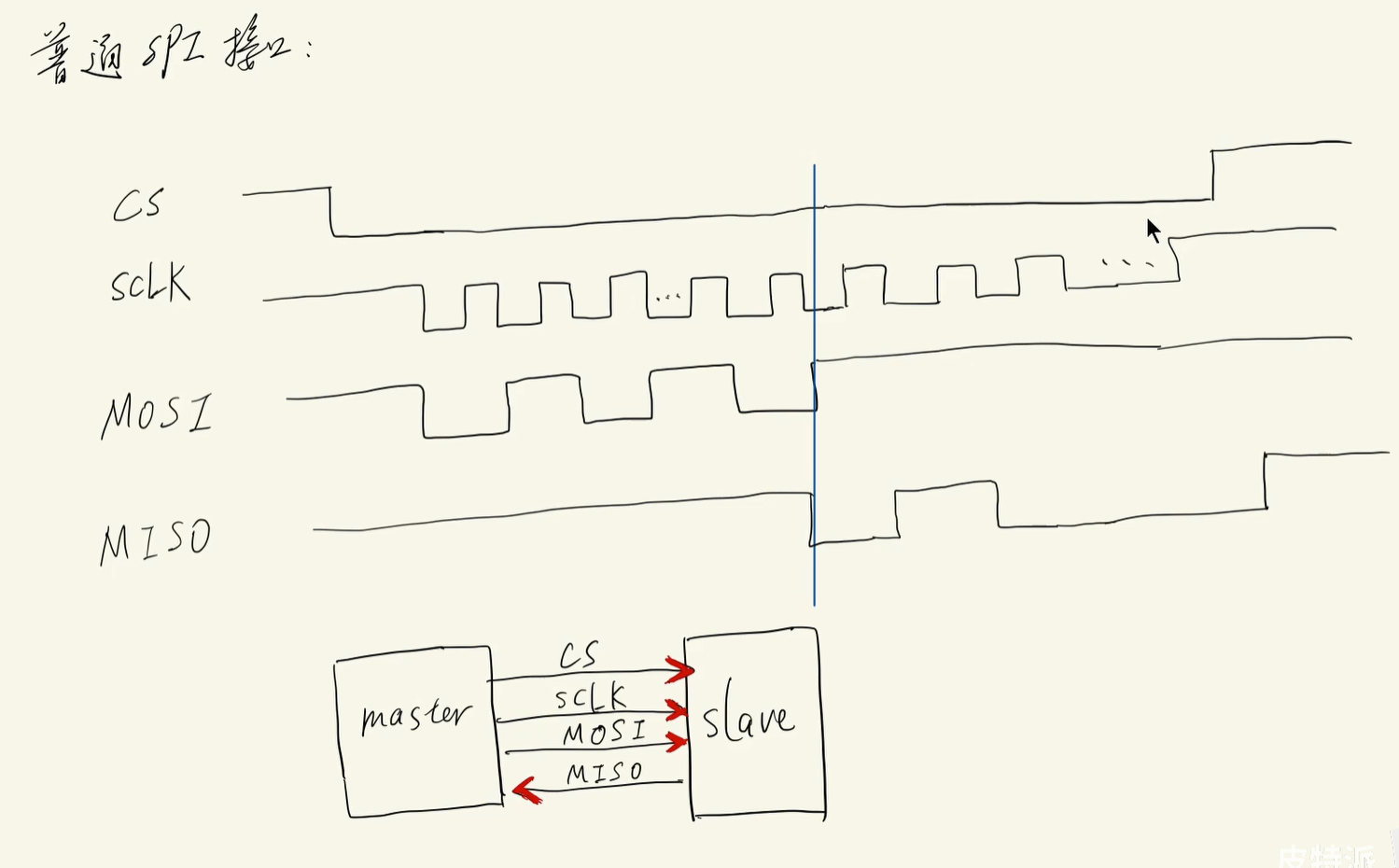

普通SPI 接口 50 MHz

-

CS 和 sclk 的第一个变化沿(和最后一个) 的时间差在芯片制造的时候是有要求的,尽量保证CS 和SCLK 的第一个变化沿要有一个时钟周期!

-

一个CS 的命令 和另一个CS 的命令之间最好停留间隔 3个SCLK 的时间,

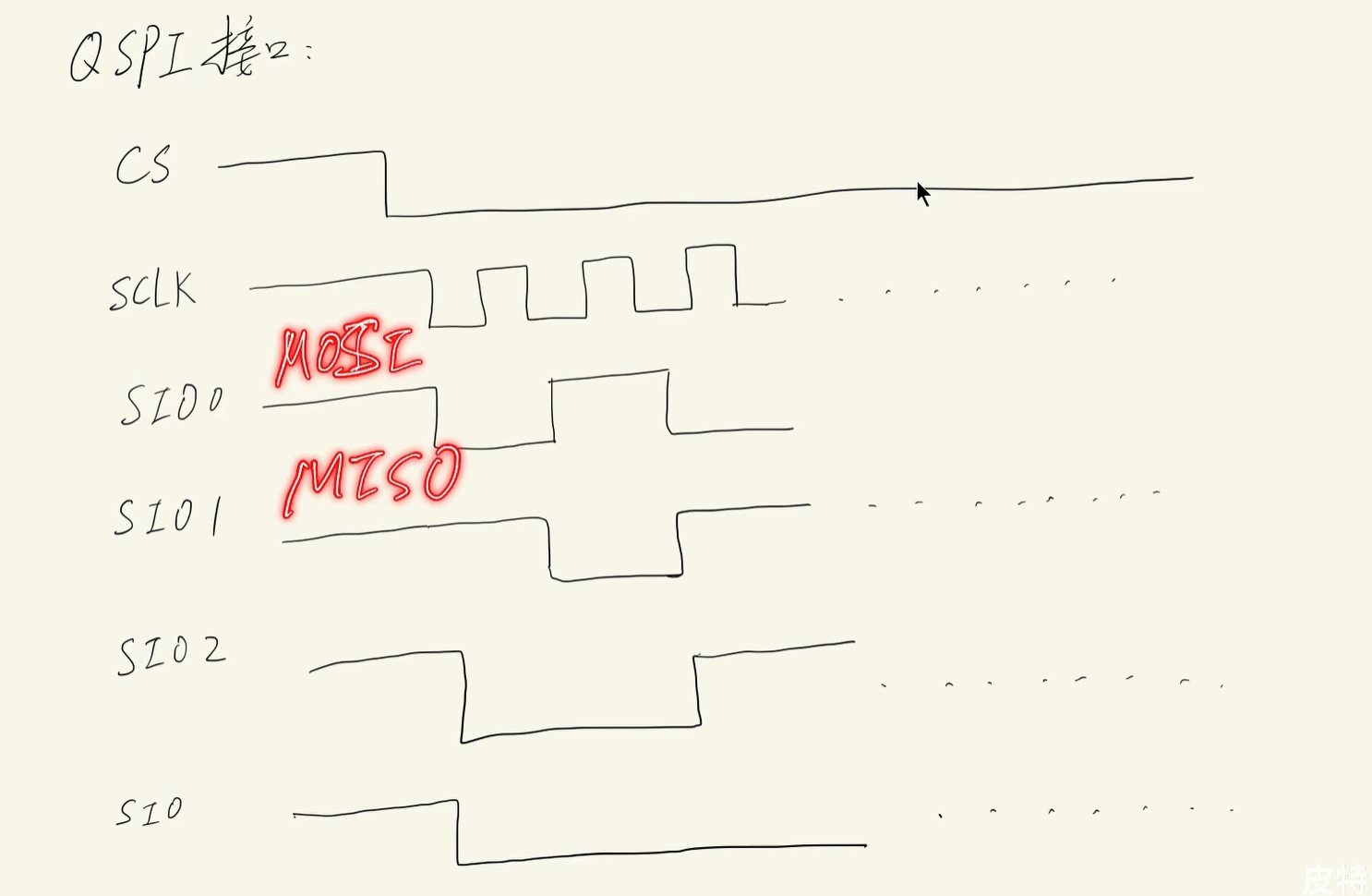

四路高速SPI QSPI接口 100Mhz

四路高速SPI 的pin 脚是双向的pin 对芯片要求比较高,四路可以同时传输。

用于XIP操作,啥是XIP? CPU 大型的指令下,CPU 会把部分指令存在 sram中,用的时候去sram 取。而XIP 技术直接从flash 进入到CPU 中。(TIP:这里的I 是 instruction 指令的意思)

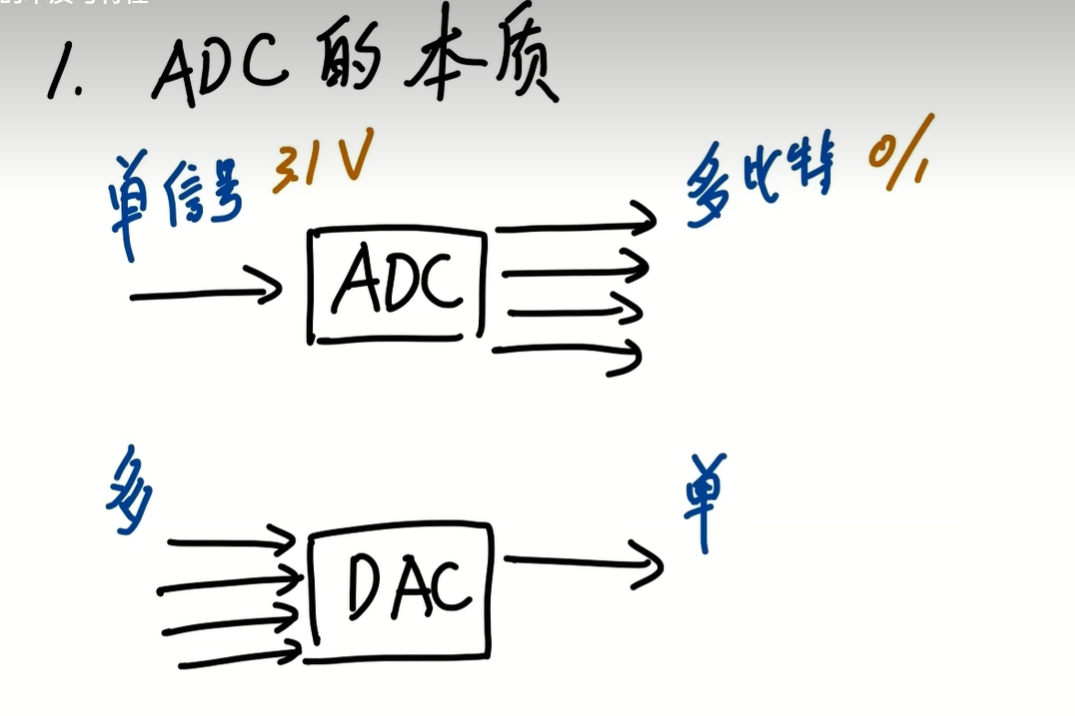

ADC 的本质

- ADC 的本质: ADC 是单信号转多比特的器件

- DAC 的本质:是多比特转单信号的器件

类似于下图的 3.1v 这个数据转化为 0/1 的电信号